Field Programmable Gate Array (FPGA) based implementation of efficient RC6 block cipher

Abstract

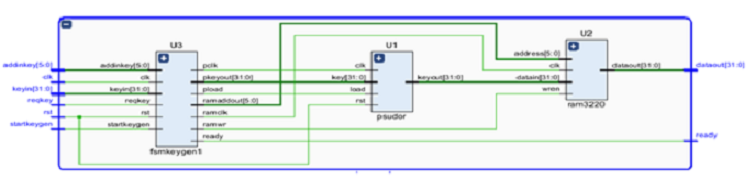

The efficient encryption system is required to achieve goal of security services. Rivest cipher 6 is a symmetric key block cipher which incorporates data dependent rotations. RC6 is specified as RC6-w/r/b, where the parameters w, r, and b respectively express the word size (in bits), the number of rounds, and the size of the encryption key (in bytes). In current work, optimized RC6 is implemented using xc7vx330t-2-ffg1157 field programmable gate array with proposing of inclusion of RC6-32/20/16. High value of rounds creates more diffusion and enables more security. Proposed system is synthesized and implemented on virtex7 field programmable gate array. The proposed method has less resource utilization and high throughput. Resource utilization in terms of slices is only 1% and in terms of fully used LUT-FF pair is 15%. Throughput of proposed system is 99.22 Gbps and efficiency is 50.596 Mbps/slice. Security analysis by performing avalanche test and strict avalanche criterion is also done. Average Avalanche effect of 54.71 is achieved, which satisfies criteria of SAC.

Keywords

RC6; Avalanche effect; FPGA; throughput; barrel shifter; security; encryption;

ISSN 2321-4635

ISSN 2321-4635